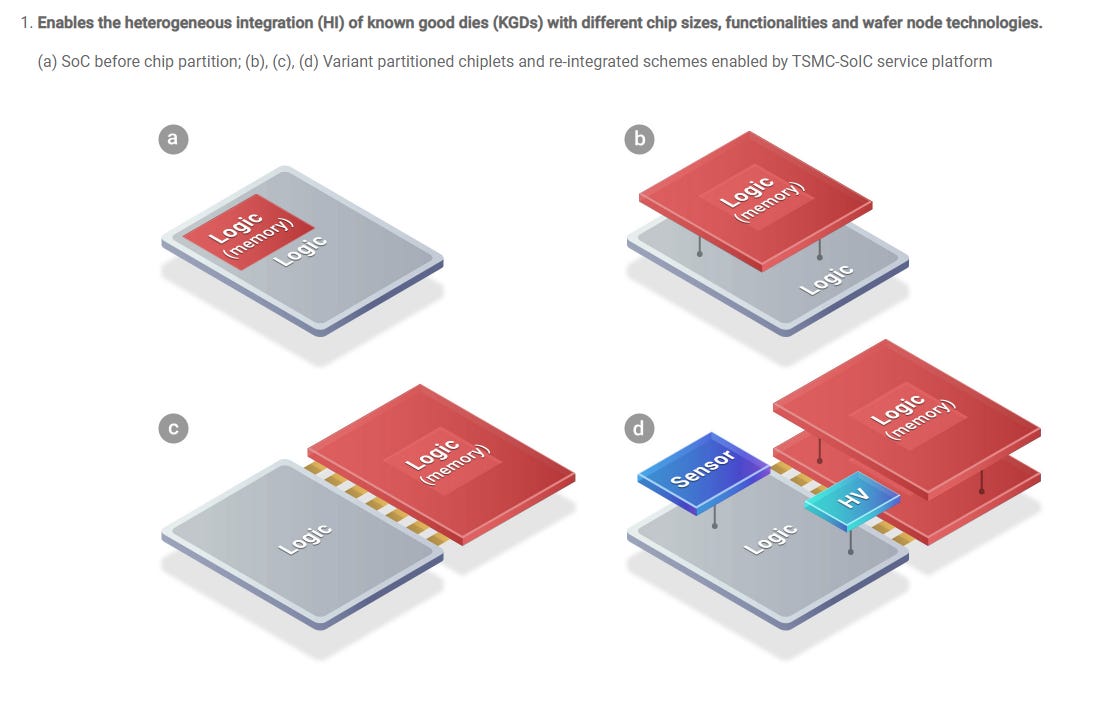

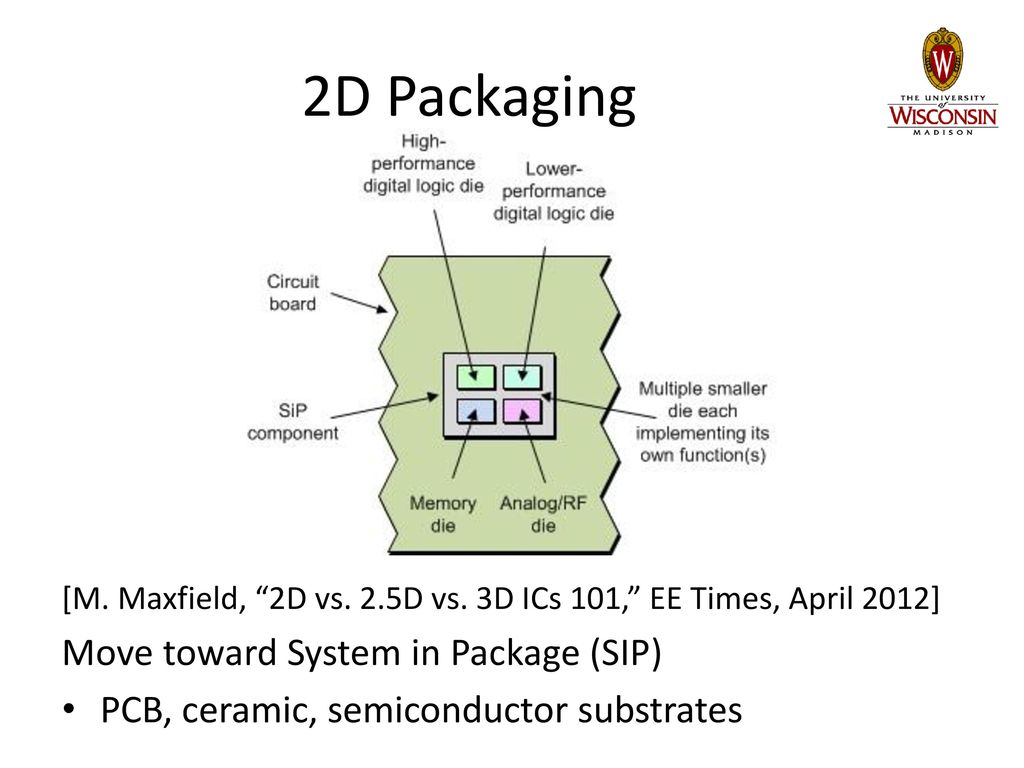

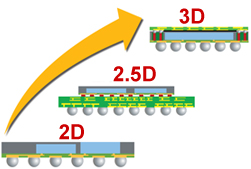

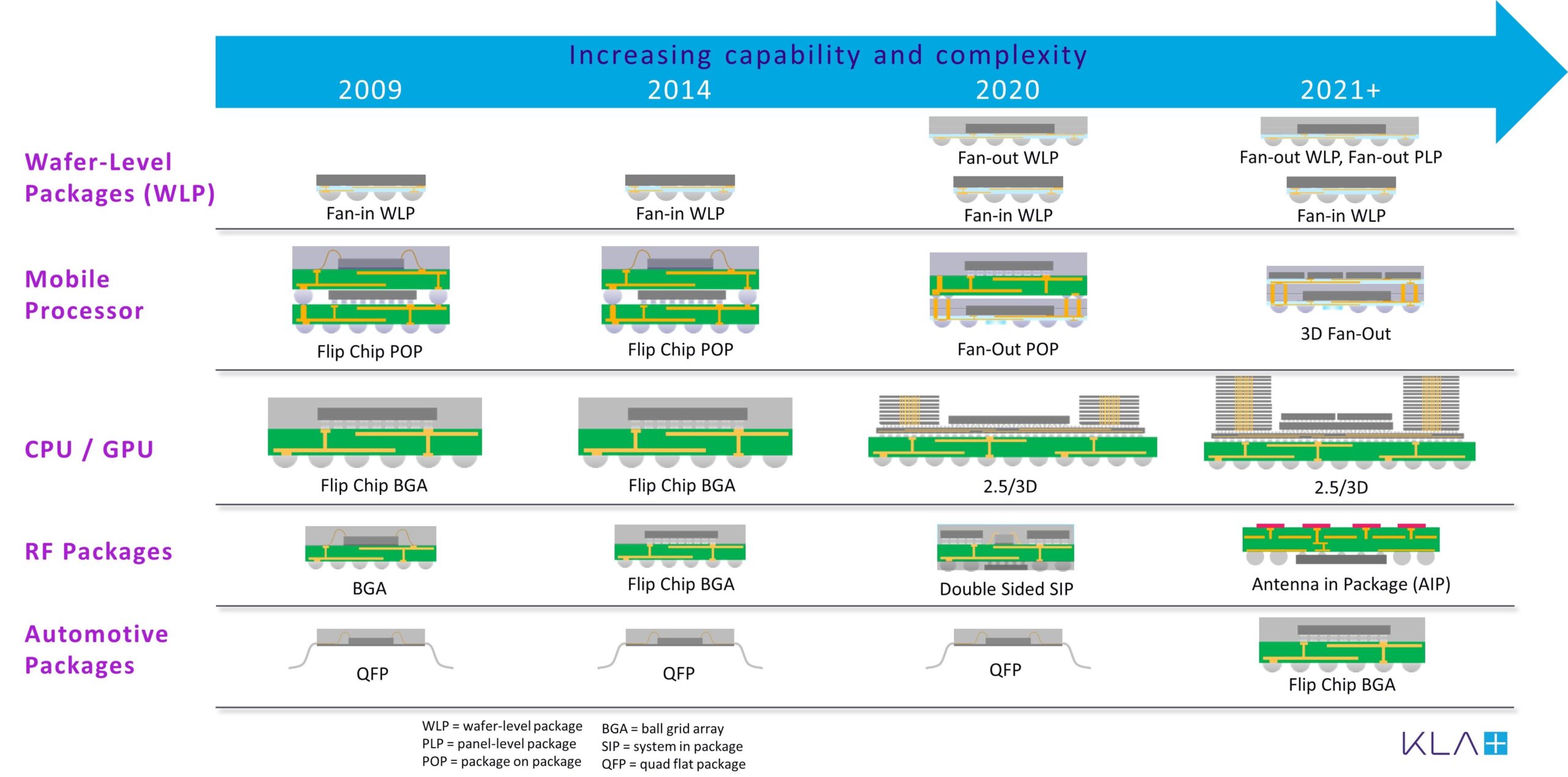

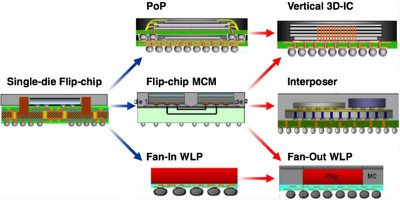

25D vs Fanout Chip on Substrate WeiHong Lai 12/8/ Technology The demand for high bandwidth and highperformance applications such as networking, AI computing and GPU IC chips are driving innovative developments in advanced IC packaging Heterogeneous integration enables the integration of multiple chips using fine line/space3D packaging refers to 3D integration schemes that rely on traditional methods of interconnect at the package level such as wire bonding and flip chip to achieve vertical stacks What is the difference between 3D Packaging, 25D interposers, and 3D ICs?

Fan Out Chip On Substrate Ase Group

2.5 d vs 3d packaging

2.5 d vs 3d packaging- Overall Risk, currently Lower 25D needs fewer new capabilities Need for standards Lower VerticalstackingMorecoordination 25D and 3D The growing adoption of 25D/3D package technologies offers unique "More than Moore" opportunities for PPA/V and costoptimized system implementations Early 25D/3D designs used disjoint tool flows, within limited system planning exploration options A unified platform, flow manager and model database are needed to provide users with the

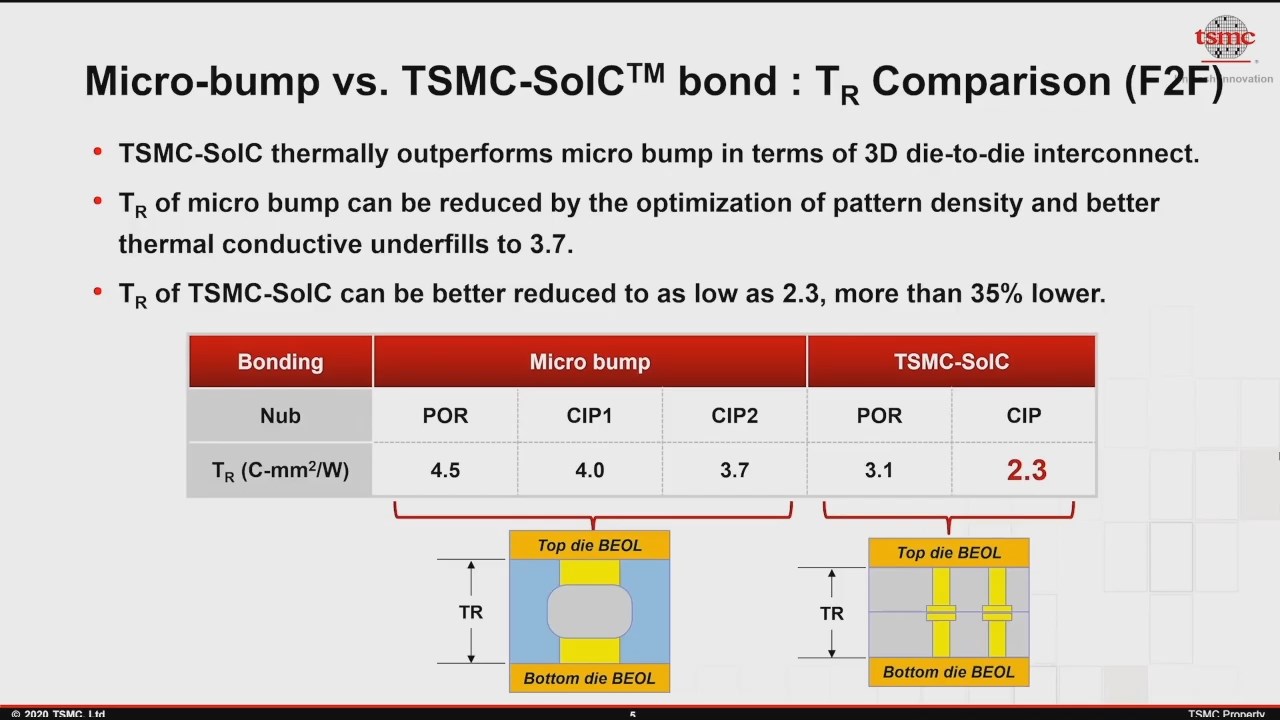

Iftle 454 Tsmc Exhibits Packaging Prowess At Virtual Ectc 3d Incites

Madden "The idea that you need true 3D stacking is a problem in the industry it's the great being the enemy of the good Yeah, it's great to say you're going to stack 3 dies on top of each other What you've done is transferred the problem to another guy, the packaging guy" How important is it to have 3D die stacking vs the 25D approach?Tong expects commercialization of 25D chip technology to take place in two years Tong notes that 25D IC should notbe regarded as a transitional integration technology" Si Interposer "25D will enable packaging of chips in the 3222 nm nodes where the fragile mechanical stability of the lowK dielectrics used in these products will require

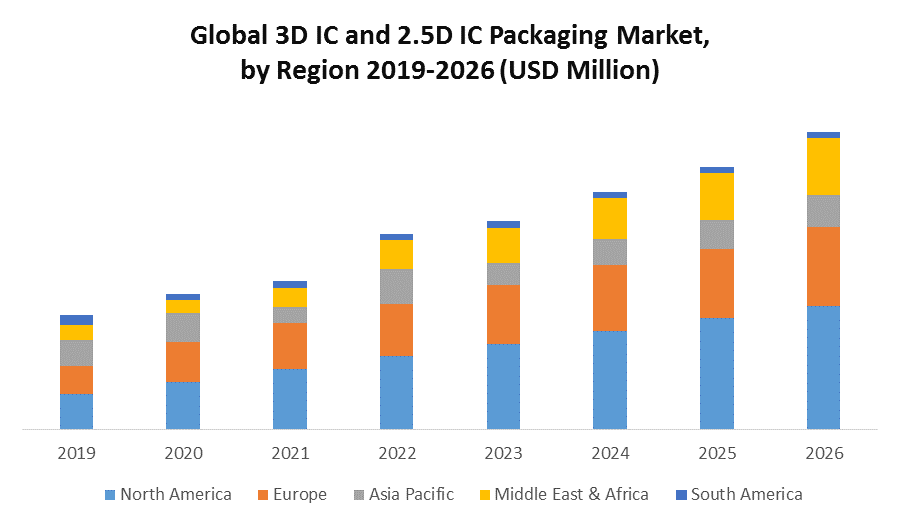

最も人気のある! 25 d vs 3d packaging What is the difference between 3D Packaging, 25D interposers, and 3D ICs?Current Developments in 3D Packaging With Focus on Embedded Substrate Technologies March 15 1 Embedding in PCBs & Inorganic Substrates 2 High Temp DieAttach & HighLead Solder 3 Thermal Management 4 PackagingThe major factors driving the 3D IC and 25D IC market for 3D TSV include highest interconnect density and greater space efficiencies in 3D TSV compared to all other types of advanced packaging, such as 3D WLCSP and 25 D Logic market accounted for the largest share of the 3D IC and 25D IC market in 15Most simple CAM programs deal with 25D parts Working in three dimensions (3D) means that you have the ability to control at least three axes simultaneously 3D contouring can then be accomplished by creating curves that use all three axes at once, like in a helical cut You will most often need a full CAM program to create gcode files

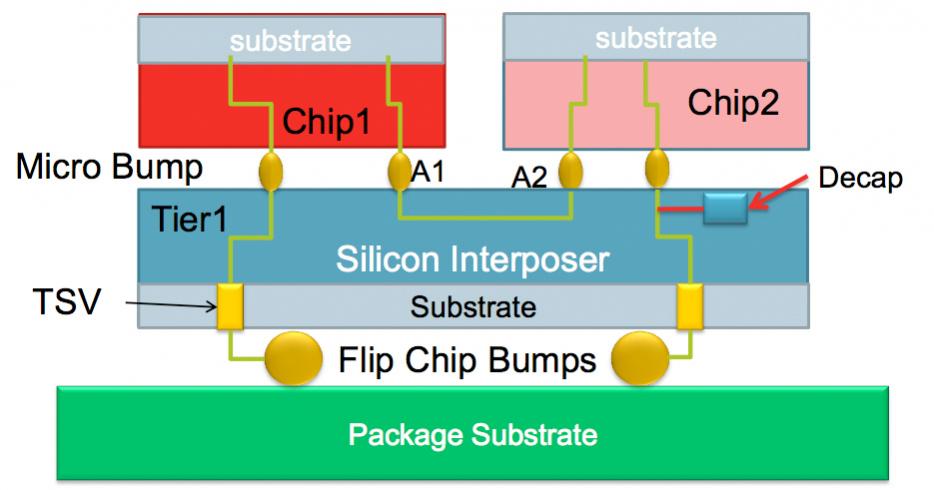

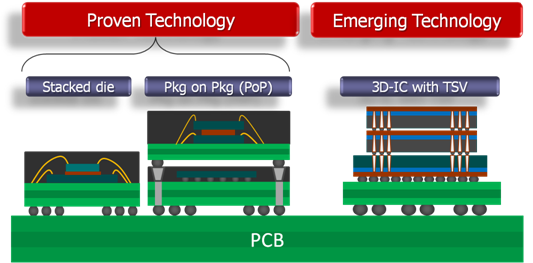

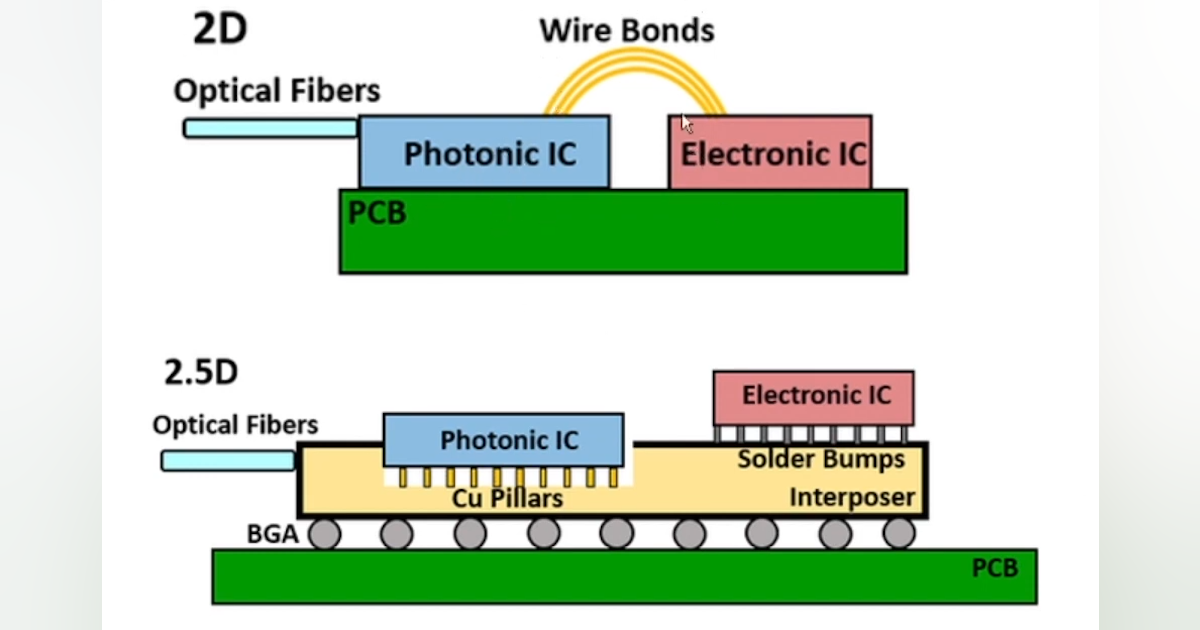

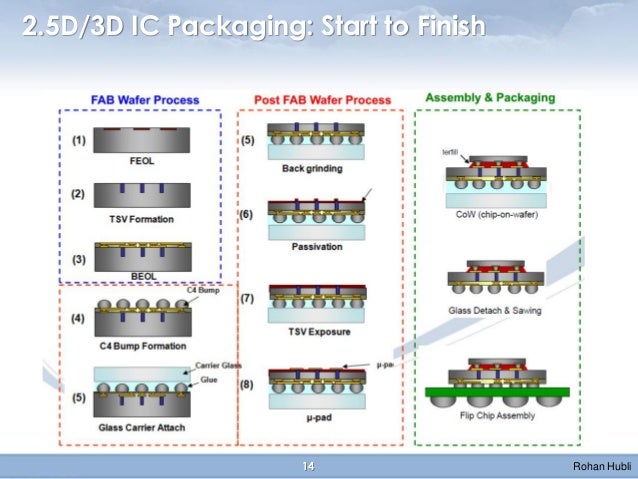

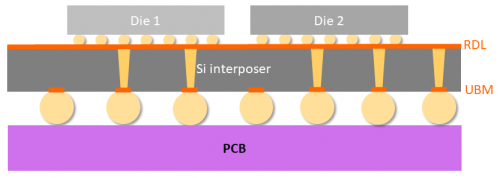

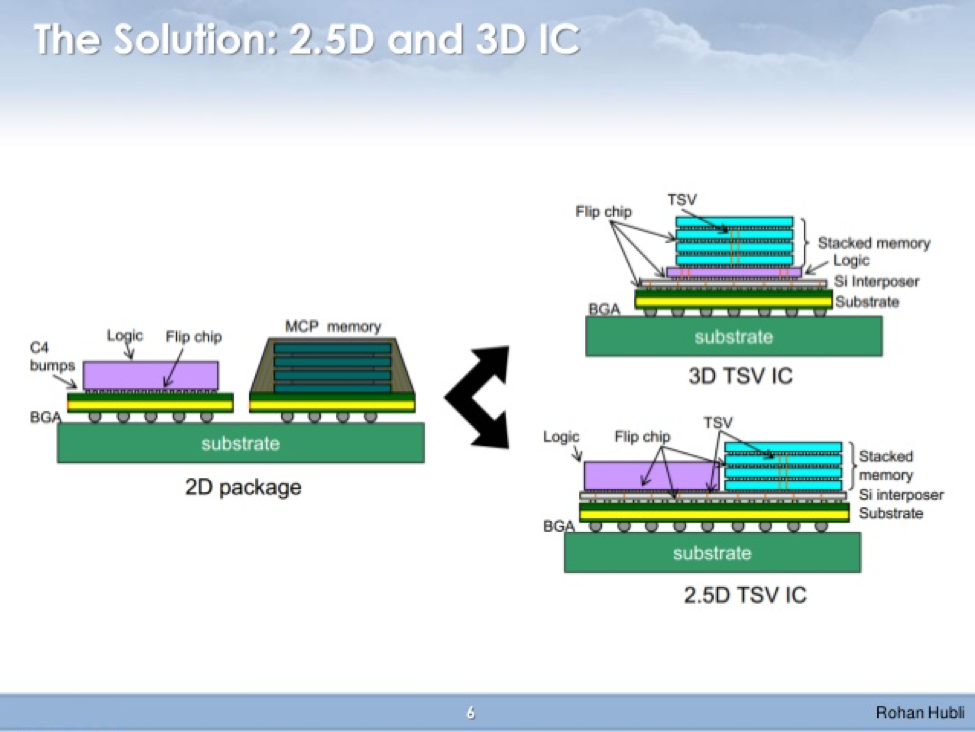

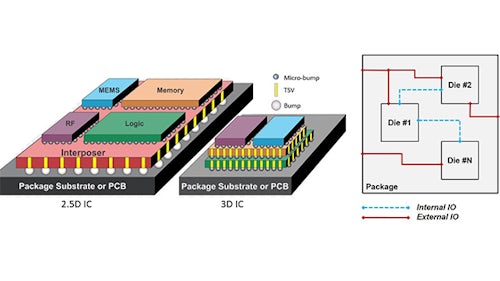

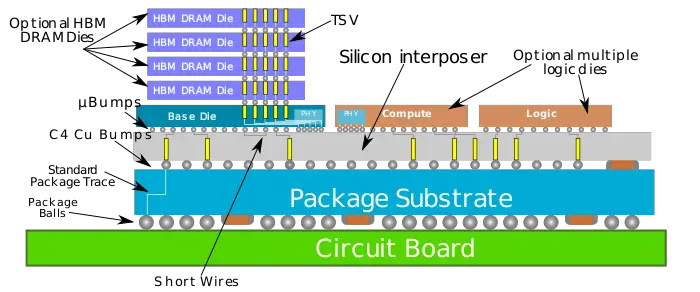

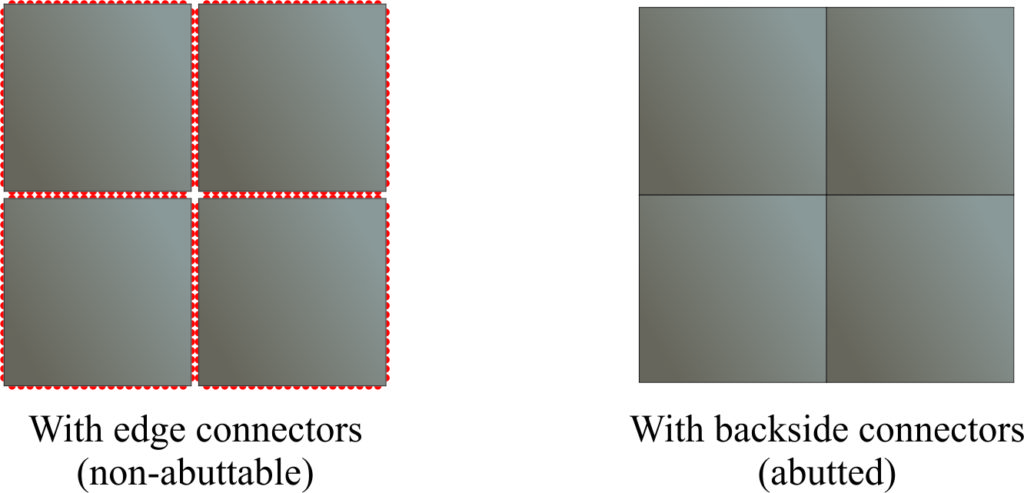

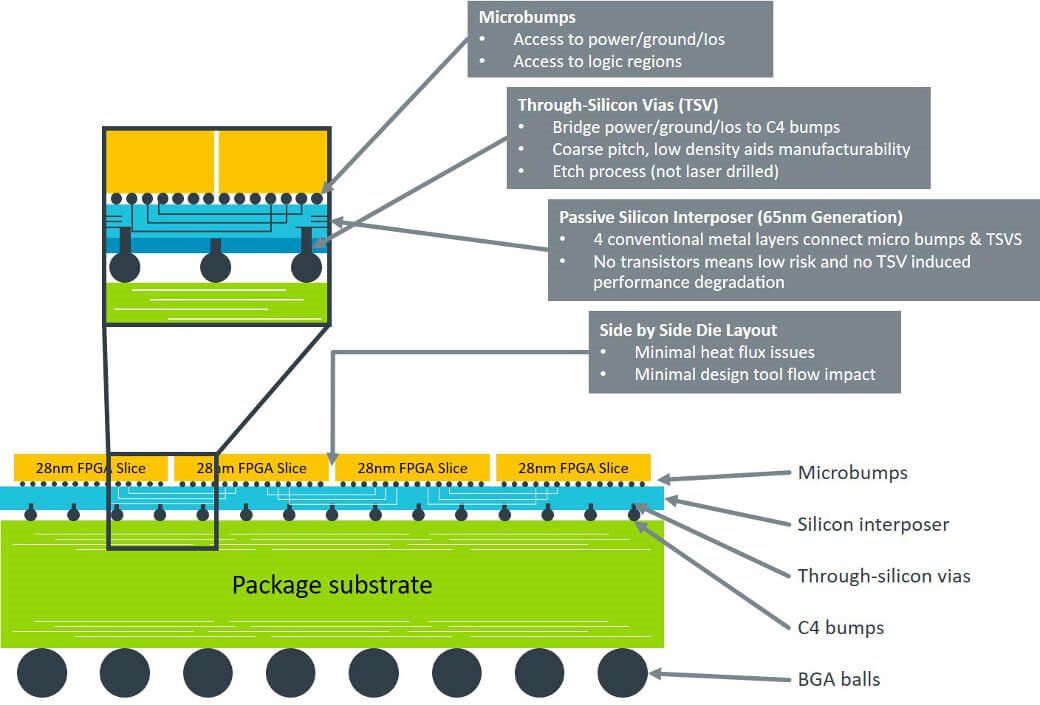

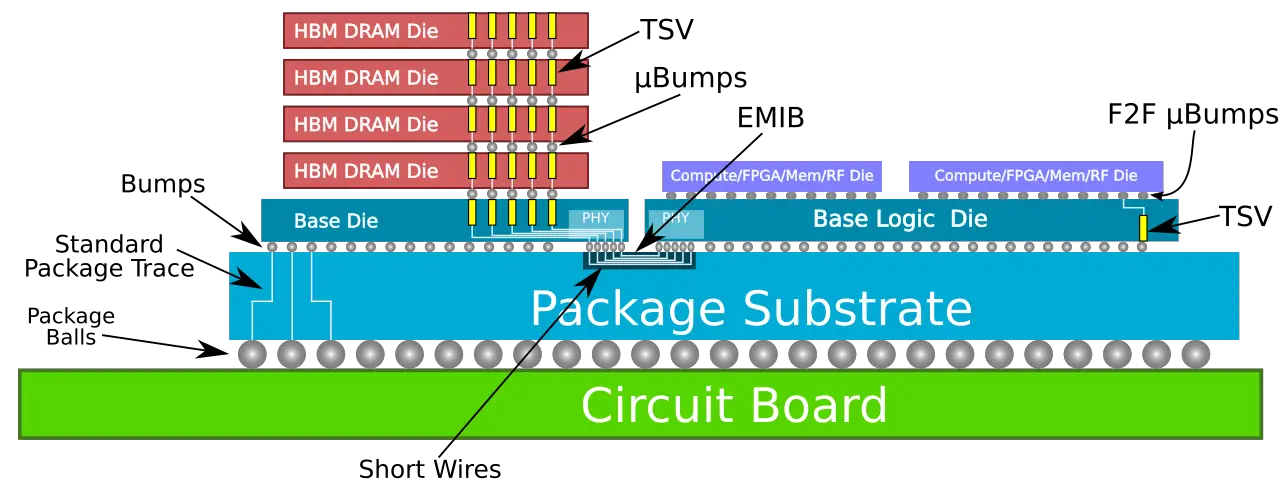

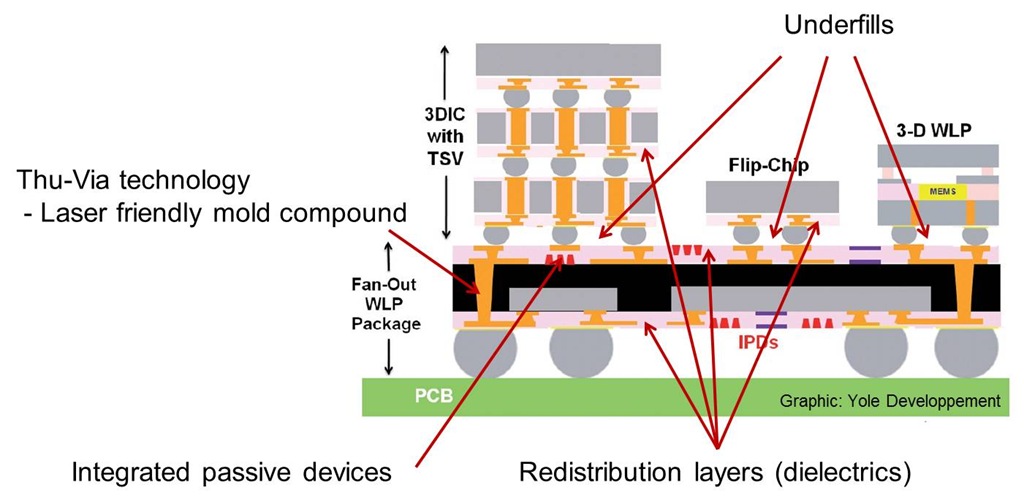

Through Silicon Via (TSV) interconnects have emerged to serve a wide range of 25D TSV and 3D TSV packaging applications and architectures that demand very high performance and functionality at the lowest energy/performance metric To enable the use of TSVs in 25D/3D TSV architectures, we have developed several backend technology platforms to 25D packaging In 25D packages, dies are stacked or placed side by side on top of an interposer based on throughsilicon vias (TSVs) The base, an interposer, provides connectivity between the chips An incremental step from traditional 2D IC packaging technology, 25D packages enable finer lines and spaces25D packaging using silicon interposers with TSVs is an incremental step toward 3D packaging

High Performance Packaging Industry Focus And Intel Foveros

3d And 2 5d Packaging Assembly With Highly Silica Filled One Step Chip Attach Materials For Both Thermal Compression Bonding And Mass Reflow Processes Semantic Scholar

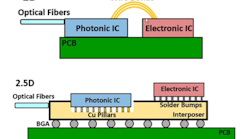

Packaging Technologies GF Si nodes are qualified in a wide range of package technologies including 2D wirebond designs, flip chip, WLCSP and FOWLP configurations, as well as 25D, 3D and SiPhotonics The 25D package technologies leverage GF TSV Si interposer technology using 65nm and 32nm process node design rules,25D Virtex7 HT @ 28Gbps Other Monolithic FPGA @ 25Gbps Eye Comparison 25D vs Monolithic Parameter Virtex7 HT Other Monolithic FPGA Data Rate 28Gb/s 25 Gb/s Data Pattern PRBS31 PRBS7 Eye Opening >2X more Less than ½ Signal Quality Clean Jitter NoisyHighend performance Packaging 3D/25D Integration Sample wwwyolefr © TABLE OF CONTENTS Part 1/2 o Package ASP split by technology 85 o Market value split by technology o 3D SoC o 3D stacked memory o 25D interposers o UHD FO o Embedded Si bridge o Chapter conclusion 94 Market trends 96 o Cloud & edge computing 97

Packaing Part 4 2 5d And 3d Youtube

More 2 5d 3d Fan Out Packages Ahead

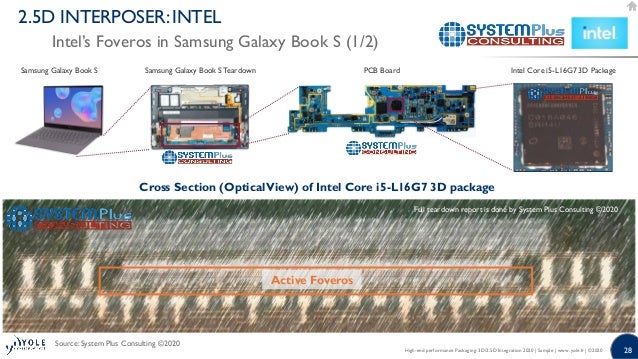

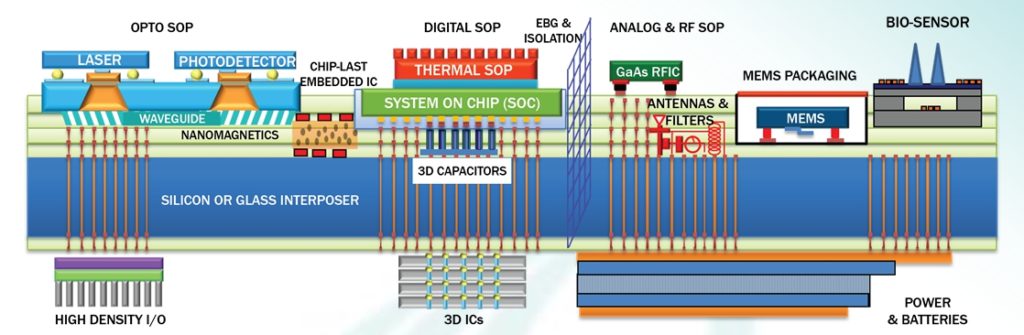

In the packaging field, 25D and 3D stacking technologies were preferred by many semiconductor players, and through silicon via (TSV) was the initial stacking technology After several years ofdevelopmentandafocusonMEMS,itfinallyentered many applications Today, 25D and 3D stacking technologies are the only solution that meet the requiredDavid Schor 25D packaging, 3D packaging, CoEMIB, EMIB, Foveros, Intel A look at ODI, a new family of packaging interconnect technologies that bridges the gap between Intel's EMIB (25D) and Foveros (3D) by providing the flexibility of an EMIB in 3D with additional benefits of thermal & power Read more There has been enough interest stirred up in R&D around glass as a lowcost alternative interposer substrate material compared with silicon, that there was an entire session dedicated to developments in that area at the 12 IMAPS International Device Packaging conference, held March 58 in Scottsdale, AZ Rao Tummala, of Georgia Tech's 3D Packaging

Iftle 468 Samsung Advanced Packaging At The Virtual Iwlpc 3d Incites

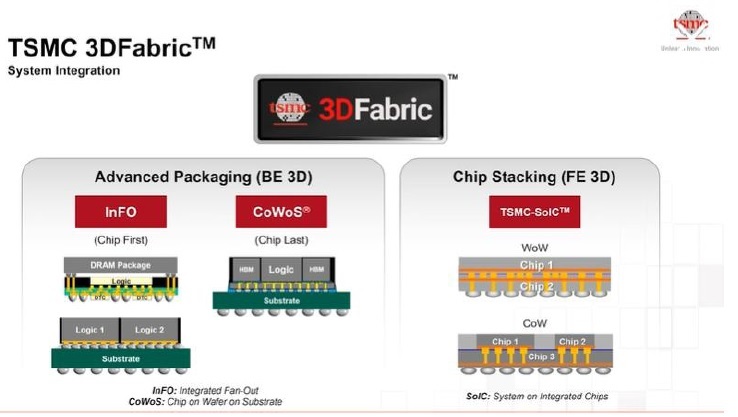

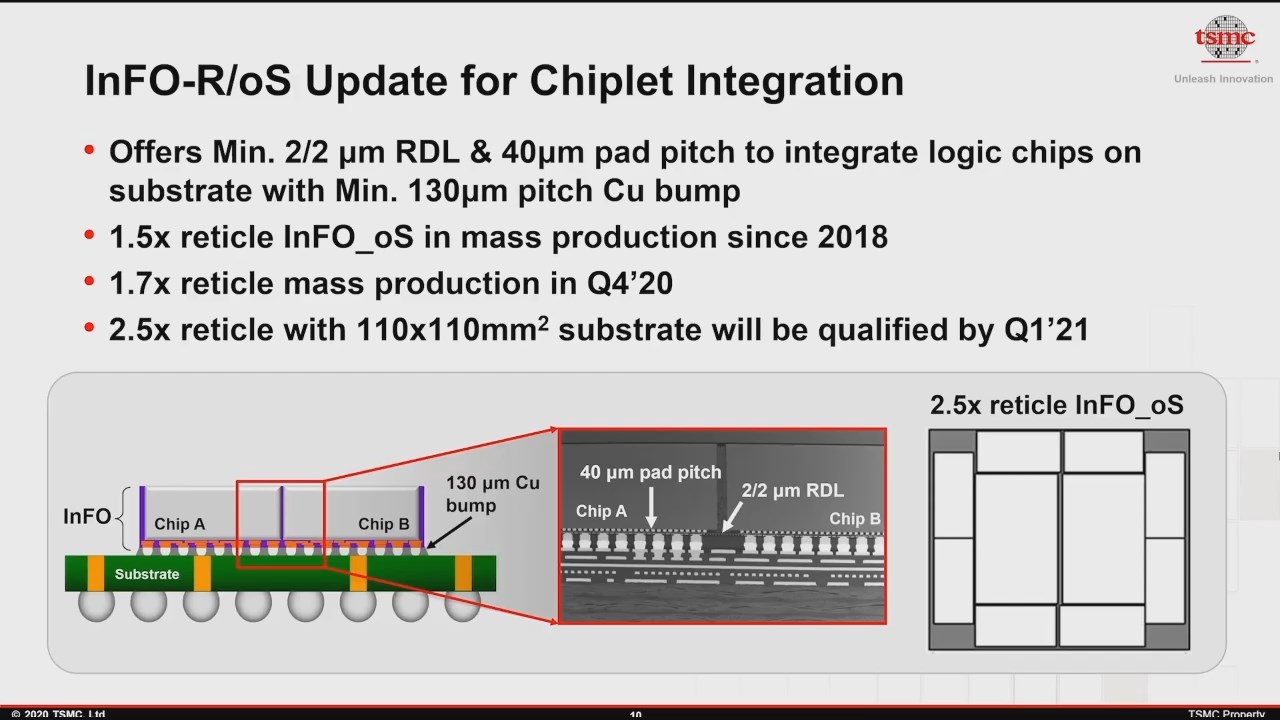

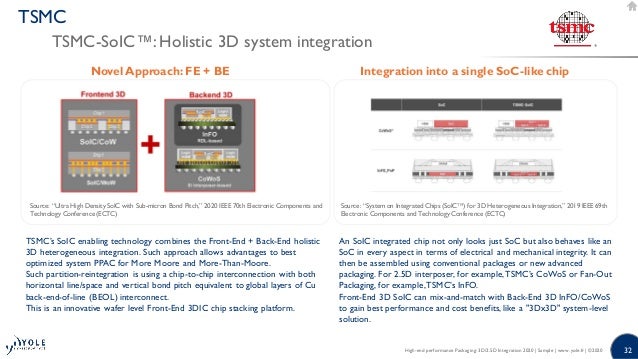

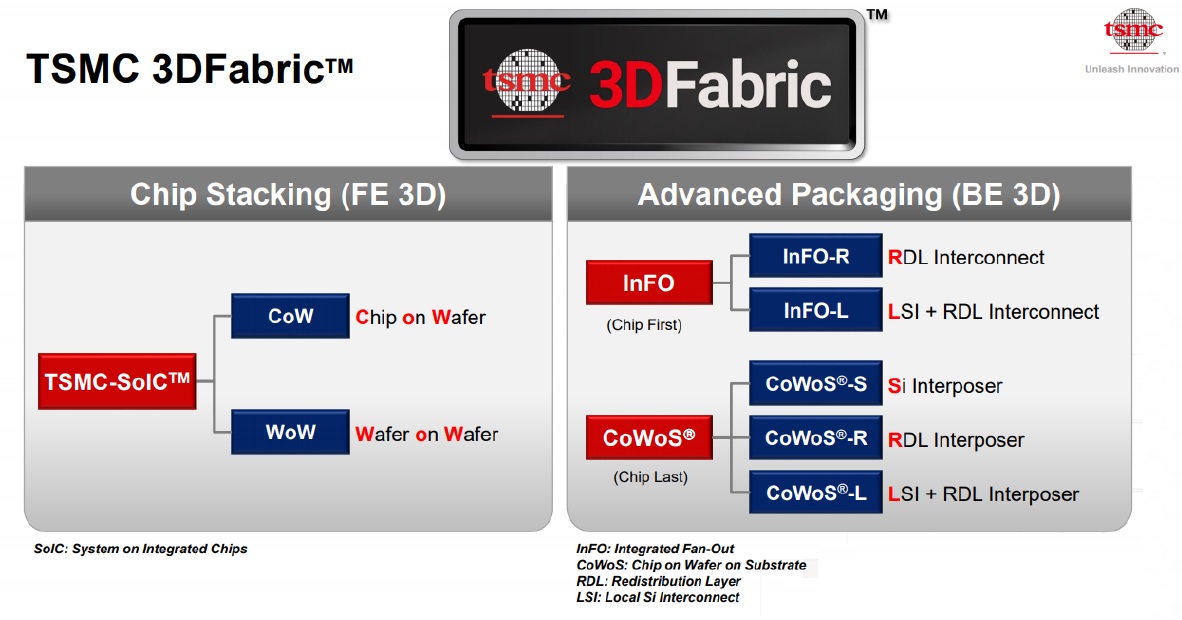

Semicap Primer Packaging History And Primer By Mule Fabricated Knowledge

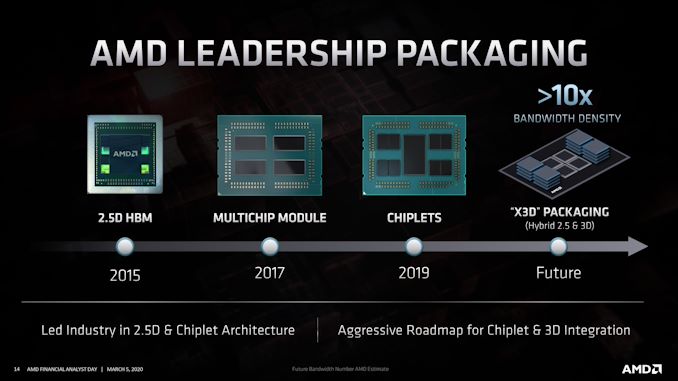

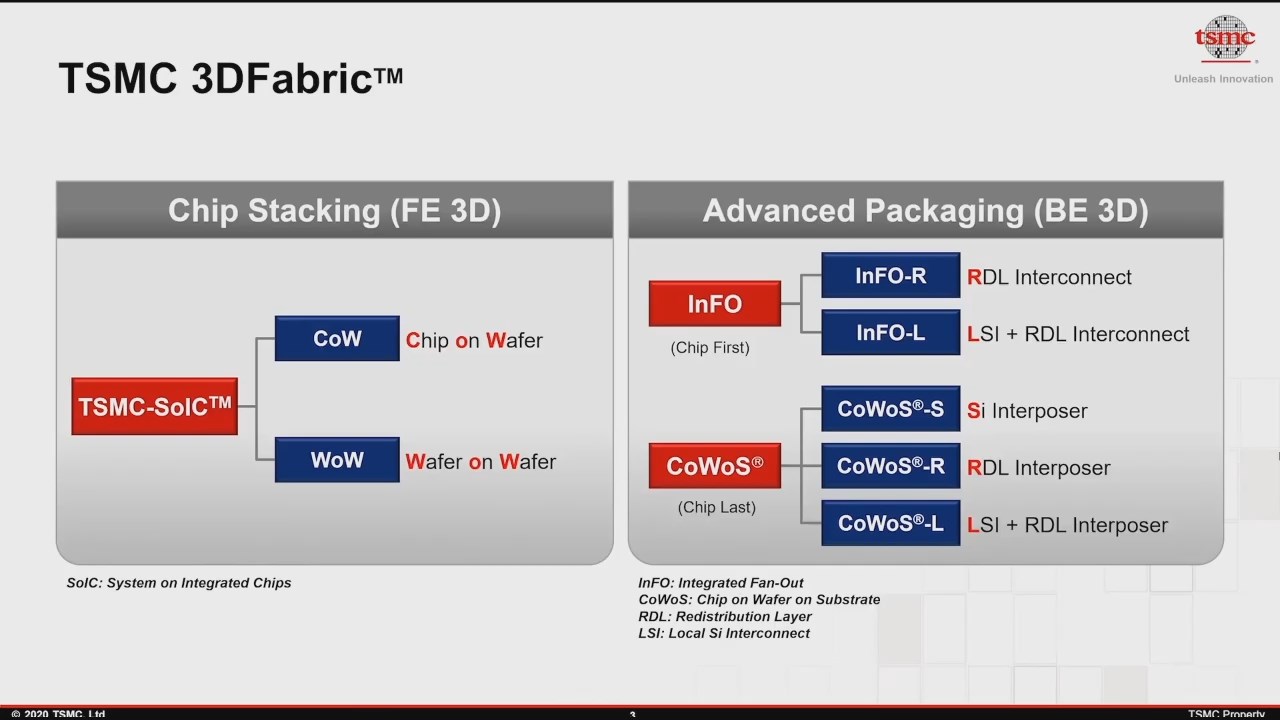

• This report is an update of the previous 17 release "3D TSV and 25D business update Market and Technology trends 17" • The scope of this report is to present the actual trends and their impact on the packaging need and especially the 25D/3D stacking technologies In order to unify all the different names it gives to its variants of its 25D and 3D packaging, TSMC has introduced its new overriding brand 3DFabric 3DFabric makes sense as a brand to tie the 2D vs 25D vs 3D ICs 101 By Max Maxfield 6 I see a lot of articles bouncing around the Internet these days about 25D and 3D ICs One really good one that came out recently was 25D ICs are more than a stepping stone to 3D ICs by Mike Santarini of Xilinx On the other hand, there are a lot of other articles that have "3D ICs

Conventional Process Flow For 2 5d 3d Ic Integration Chip On Download Scientific Diagram

Sorting Out Packaging Options

3D System on Chip * √ √ Silicon photonics √ √ √ √ 3D Stacked IC find their place in performance demanding applications * 3D System on Chip consists in logiconlogic and memoryonlogic stacked 3D ICIn this presentation we clarify one of the most confusing topics in xray inspection the difference between 2D, 25D, and 3D xray inspection Check the slides to see if you can tell if an image is 2D, 25D, or 3D! According to AMD, 21 will mark the first introduction of its 3D Chiplet architecture design We've already seen 2D and 25D packaging on consumer and server products but with 3D VCache, we are

Mcm Sip Soc And Heterogeneous Integration Defined And Explained

2 5d 3d Tsv Processes Development And Assembly Packaging Technology Semantic Scholar

Is included to determine packaging and cooling costs We then use this model to explore and characterize the design space for the emerging integration options We also present the best choice between different 2D, 25D, and 3D partitioning schemes across the range of highperformance power densities and gate counts II COST ANALYSISMETHODOLOGYA 25D integrated circuit (25D IC) combines multiple integrated circuit dies in a single package without stacking them into a threedimensional integrated circuit (3DIC) with throughsilicon vias (TSVs) The term "25D" originated when 3DICs with3D TSV and 25D Market Growth, Trends, COVID19 Impact, and Forecasts (21 26) The 3D TSV and 25D Market is segmented by Packaging Type (3D Stacked Memory, 25D Interposer, CIS with TSV, 3D SoC), Enduser Application (Consumer Electronics, Automotive, HighPerformance Computing, and Networking), and Geography

2 5d Ics Or Interposer Technology Youtube

2 5d And 3d Designs Semiwiki

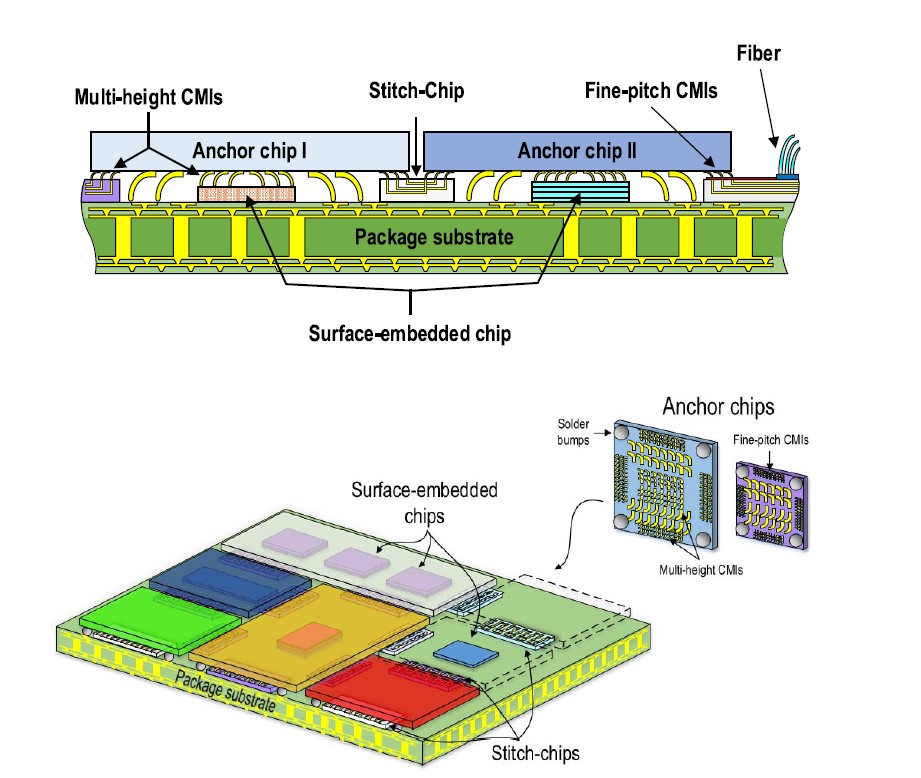

ASE is one of the pioneers in 25D/3D packaging technology and has successfully introduced the mass production of the world's first 25D IC package equipped with High Bandwidth Memory (HBM) 25D refers to die stacking package using interposers to achieve the best performance of internet connectivity25 d vs 3d packaging 25 d vs 3d packagingAnd 3D systems integration This video, 3D Chip Technology for Dummies, from Applied Materials, breaks it down in very easy25D/3D TSV Meet high performance, low energy demands Through Silicon Via (TSV) interconnects have emerged to serve a wide range of 25D TSV and 3D TSV packaging applications and 25/3D Level Heterogeneous Integration • Heterogeneous Integration • In the context of describing 25D/3D packaging level of technology • Integrating dissimilar chips using a packaging technology with I/O density higher than organic substrate (Feature size smaller than organic substrate, or 3D die) • Technology drivers • High bandwidth

2 5d 3d Ase Group

Typical Structure Of 2 5d Ic Package Utilizing Interposer Not To Scale Download Scientific Diagram

25D is a packaging methodology for including multiple die inside the same package The approach typically has been used for applications where performance and low power are critical Communication between chips is accomplished using either a silicon or organic interposer, typically a chip or layer with throughsilicon vias for communication The overall IC packaging market is projected to reach $68 billion in 19, up 35% over 18, according to Yole Développement Of those figures, advanced packaging is projected to grow at 43% in 19, compared to 28% for traditional/commodity packaging, according to Yole More 25D/3D and chiplets IC packaging is important for several reasons In conclusion, 3D/25D packaging has now become an essential part of the semiconductor industry, extending Moore's Law at systemlevel The 3D/25D integration is accelerating 3D interconnect density (3D ID) into new highs Such is the value of 3D/25D packaging A strong adoption of endsystem units in cloud computing, networking, HPC, and

Amd Discusses X3d Die Stacking And Packaging For Future Products Hybrid 2 5d And 3d

Iftle 468 Samsung Advanced Packaging At The Virtual Iwlpc 3d Incites

25D & 3D Packaging Cost Model Which applications are right for this technology?25D / Extended eWLB JCET's eWLased interposers enable very dense interconnection with more effective heat dissipation and improved processing speed in a proven, lowwarpage packaging structure A 3D eWLB interconnection (including Si partitioning) is accomplished by means of a unique facetoface bonding approach which eliminates the need for more expensiveShorter distances allow electronic signals to travel more quickly from one component to another, so a 25D assembly can demonstrate higher performance than an equivalent circuit board Power Like 3D ICs, 25D assemblies save power by using shorter connections

Highlights Of The Tsmc Technology Symposium 21 Packaging Semiwiki

Samsung Announces 2 5d Integration Solution I Cube4 For High Performance Applications

AMD and Intel unveiled 3D packaging technologies for the circuits at Hot Chips 33 Both AMD and Intel are currently walking the same path toward 3Dpackaged chips with direct copper contacts between the chips In recent years, packaging technologies have become increasingly important in the manufacture of efficient circuits 5221 Major Benefits of 25D Ic Packaging Over the Traditional 2D Packaging Practices 523 3D Ic Packaging Technology 524 2D Vs 25D Vs 3D Ic Packaging Technology 53 System in Package (SIP 25D packaging In 25D packages, dies are stacked or placed side by side on top of an interposer based on throughsilicon vias (TSVs) The base, an interposer, provides connectivity between the chips An incremental step from traditional 2D IC packaging technology, 25D packages enable finer lines and spaces

2 5d

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

In this paper, we will examine new advances in packaging technology to maintain the IC scaling edge, as well as the role of new emerging 25dimensional (25D) and 3dimensional (3D) IC packaging platforms for addressing the gap seen between the slowdown of Moore's Law scaling and the everincreasing system integration requirementsChip Packaging Part 4 25D and 3D Packaging Dr Navid Asadi's group examines 25D and 3D packaging for expanding capabilities and capacities of chip solutions Peter Xi2D, 21D, 25D, and 3D Package Studies in NEPP Eric J Suh Joseph Riendeau Jet Propulsion Laboratory, California Institute of Technology NASA Electronic Parts and Packaging Program (NEPP) 19 Annual NEPP Electronic Technology Workshop (ETW) June 18th, 19 1

2 5d Vs 3d

Technology Challenges Ece Cs 752 Fall Ppt Download

With 25D/3D packaging this extends Moore's Law at systemlevel Times have changed The industry is seeking alternatives to design and manufacture the latest Systems on Chips (SoCs) using System in Package (SiP) and chipletbased approaches by leveraging highend packaging to mix both the latest and mature nodes 25D/3D packaging is Threedimensional (3D) packaging with throughsiliconvias (TSVs) is an emerging technology featuring smaller package size, higher interconnection density, and better performance;The material presented will also reference 3D packaging standards and recognize innovative technologies from a number of industry sources, roadmaps and market forecasts Key words 25D, 3D Semiconductor Package Technology, Through Silicon Via, TSV, Through Glass Via, TGV

Iftle 454 Tsmc Exhibits Packaging Prowess At Virtual Ectc 3d Incites

Advanced Packaging Confusion Athisnews

Use the model to for your product Include supplier specific details and incoming die preparation in your analysis View the detailed costs—including labor, material, capital, tooling, and yield impacts—for every step Labor rate Lot size Overhead rate

The Race To Next Gen 2 5d 3d Packages

Pin On Telecharger Gratuit

The Partially Molded 2 5d Packages And Assembly On The Board In Download Scientific Diagram

Jcet Group 2 5d 3d Integration

Global 3d Ic And 2 5d Ic Packaging Market Industry Analysis

High End Performance Packaging

Flip Chip Technology Market Report 18 Segmentation By Wafer

2 5d Packaging Vs 3d Packaging Anny Zhang Indium Corporation Blogs Chip Attach Gold Solder Indium Indium Corporation

Heterogeneous Integration Hi Ase Group

Increased Funds Could Catalyze Tsmc S 3d Ic Research News

Chip Packaging Part 4 2 5d And 3d Packaging Electronic Design

Silicon Interposer Warpage Estimation Model For 2 5d Ic Packaging Utilizing Passivation Film Composition And Stress Tuning Semantic Scholar

Increased Funds Could Catalyze Tsmc S 3d Ic Research News

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Different 3d Technologies Arranged According To Manufacturing Costs And Download Scientific Diagram

2 5d 3d Ic Market Challenges Opportunities

About 2 5d Technology Nhanced Semiconductors Inc

2 5d And 3d Ics New Paradigms In Asic Product Engineering Blog Einfochips

Advanced Packaging Five Trends To Watch In 17 Electronic Products

3d Ic And 2 5d Ic Packaging Market In Depth Analysis Taiwan

High End Performance Packaging

Ewh Ieee Org

System In Package Ase Group

About 2 5d Technology Nhanced Semiconductors Inc

Amd Working On Milan X Sp W Stacked Dies And Hbm Memory Hardware Times

Heterogeneous Integration 2 5d And 3d Integrated 3d Systems Group

3d And 2 5d Packaging Assembly With Highly Silica Filled One Step Chip Attach Materials For Both Thermal Compression Bonding And Mass Reflow Processes Semantic Scholar

Global 3d Ic And 2 5d Ic Packaging Market 17 Taiwan

Insights From Leading Edge Just Another Solid State Technology Sites Site Page

Fan Out Chip On Substrate Ase Group

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Design Electrical Mechanical Thermal Prc Gatech Edu Georgia Institute Of Technology Atlanta Ga

Plasma Etch And Deposition Solutions For 2 5d 3d Packaging Spts

2 5d Semiconductor Engineering

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Iftle 381 Tsmc Wow Insights From Leading Edge

Chip Packaging Part 4 2 5d And 3d Packaging Electronic Design

1

Southeast Asia Ems And Printed Circuit Boards Assembly News

Welcome To Calibre Reliability Verification Siemens Digital Industries Software

Iftle 464 Tsmc S Family Of Packaging Technologies Are Built On 3d Fabric 3d Incites

More 2 5d 3d Fan Out Packages Ahead I Micronews

3d Ic And 2 5 D Ic Packaging Industries In Depth Analysis

Interposer Wikipedia

Underfill Process Nordson Asymtek

Iftle 1 Imaps Device Packaging Conf Part 2 Amd Scp Insights From Leading Edge

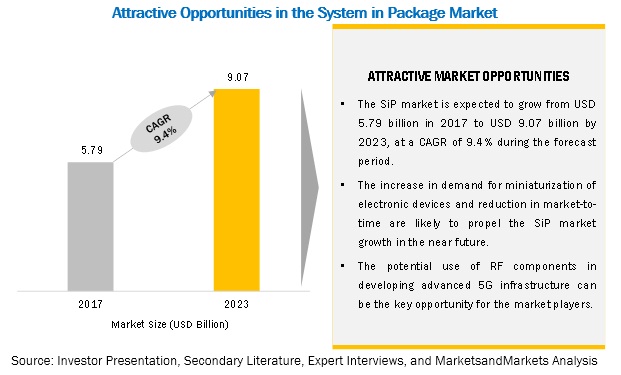

System In Package Market By Packaging Technology Package Packaging Method Device Application Covid 19 Impact Analysis Marketsandmarkets

Eps Ieee Org

Ewh Ieee Org

Highlights Of The Tsmc Technology Symposium Part 2 Semiwiki

Chip On Wafer On Substrate Cowos Tsmc Wikichip

3d Ic And 2 5d Ic Packaging Market Size Share Trends Analysis Industry Report 24 Igr

Intel Looks To Advanced 3d Packaging For More Than Moore To Supplement 10 And 7 Nanometer Nodes Page 2 Wikichip Fuse

Automated Latch Up Verification In 2 5d 3d Ics In Compliance Magazine

Advanced Packaging Five Trends To Watch In 17 Electronic Products

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

1

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

Cetimes Com

Eetimes 3d Ic Design

2d

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

3d Multi Chip Integration And Packaging Technology For Nand Flash Memories Springerlink

Circuitinsight Com

Sensors In 3d And 2 5d Nhanced Semiconductors Inc

Solutions Bi Components Pte Ltd

Integrated Circuit Packaging And Gct The Samtec Blog

The Partially Molded 2 5d Packages And Assembly On The Board In Download Scientific Diagram

Three Dimensions In 3dic Part I Research Articles Arm Research Arm Community

Intel Looks To Advanced 3d Packaging For More Than Moore To Supplement 10 And 7 Nanometer Nodes Page 2 Wikichip Fuse

17 European 3d Summit Making Advanced Packaging Great Again

Nist Gov

Advanced Packaging S Next Wave

Amkor S Advanced Packaging A Closer Look I Micronews

Polymer Challenges In Electronic Packaging Overview Polymer Innovation Blog

Packaging Wars Begin

Patent Applications Reveal Apple S Research Into 3d Chip Packaging Macrumors

Glass Packaging R D For 2 5d Rf 5g Photonics Autonomous 17 05 01 Cent Nbsp 18 Ieee Cpmt Workshop Cent Acirc Sbquo Not Acirc Euro Oelig Glass Pdf Document

Nepp Nasa Gov

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

0 件のコメント:

コメントを投稿